식각(etching) 공정에서 profile에 영향을 미치는 loading effect에 대해서 - 2

반도체의 식각(etching) 공정은 진행하고자 하는 패턴에 따라 식각 속도나 proflie에 영향을 줄 수 있는 loading effect가 발생할 수 있다. 그래서 loading effect는 식각 공정을 진행하는 웨이퍼에서 uniformity를 떨어트릴 수 있다.

loading effect 의 종류와 profile을 어떻게 진행시키는지 공부해보자.

저번 글은 Macro & Micro loading effect 에 대한 내용이었다.

2022.07.08 - [self.반도체&전자회로 공부] - 식각(etching) 공정에서 profile에 영향을 미치는 loading effect에 대해서 - 1

식각(etching) 공정에서 profile에 영향을 미치는 loading effect에 대해서 - 1

식각(etching) 공정에서 profile에 영향을 미치는 loading effect에 대해서 반도체의 식각(etching) 공정은 진행하고자 하는 패턴에 따라 식각 속도나 proflie에 영향을 줄 수 있는 loading effect가 발생할 수 있

selfimprove39.tistory.com

1. RIE-lag(reactive ion etching lag)

- RIE-lag 란?

Dry etching 공정에 있어서 식각해야하는 패턴의 폭의 길이에 따라서 식각 속도가 변화하는 현상이 있다.

폭이 좁아질수록 식각 속도가 느려지는 현상을 RIE-lag 라고 한다.

이것은 결국 패턴의 폭과 식각된 깊이의 비율이 커질수록(폭에 비해 깊이가 깊어질수록) 식각 속도가 느린 것과 같아서

Aspect ratio와 관련이 깊은 현상이라고 할 수 있다.

Aspect ratio란 식각하려는 feature의 깊이를 a, 폭을 b라고 했을 때 a/b를 말한다. (깊이와 폭의 비율)

동일한 폭에서 깊이가 깊어질수록 Aspect ratio가 커진다고 할 수 있고 깊이의 증가에 따라 Etch rate가 감소하는 현상을

Aspect Ratio Dependent Etching(ARDE) 라고 한다.

그리고 이 ARDE 현상은 반응성 이온의 충돌로 식각을 진행하는 RIE(reactive ion etching) 공정에서 확인되며, 그래서 RIE-lag 라고도 부른다.

- RIE-lag 의 발생

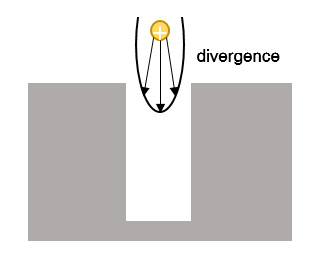

Ion 입자의 충돌 에너지로 식각을 진행하는 상황에서 위에서 부터 입사하는 이온의 flux는 모두 수직 방향으로만 내려 오는 것이 아니라 입사하는 각도에 divergence가 발생한다.

Aspect ratio가 큰 패턴과 작은 패턴을 비교하여 생각해보자.

식각하려는 패턴의 깊이가 좁고 깊어질수록 바닥면까지 도달하는 이온은 적어지게 되고

그에 따라서 충돌 에너지가 없으니 식각의 진행이 더뎌지게 되어 RIE-lag 현상이 보이게 된다.

같은 깊이에서 넓은 폭을 갖는 패턴이라면 바닥면에 도달하는 이온이 많기 때문에 식각 속도가 빠른것은 당연하다.

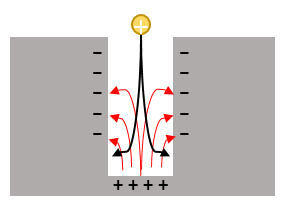

또 다른 이유로는 charging에 의한 이온 입자의 휘어짐이 있다.

전자는 이온에 비해 직진성이 떨어진다.

그래서 전자의 경우 좁고 긴 패턴의 입구 영역과 옆 벽면 영역에는 도달할 수 있지만

패턴의 안쪽 아래 끝까지 도달하는것은 어렵다.

Ion은 직진성이 강하여 식각하려는 패턴의 바닥에 도달하는 것이 비교적 쉽다.

그러면 위에서부터 패턴의 중간까지는 음의 전하(-)로 대전이 되고, 바닥면은 양의 전하(+)로 대전이 되게 된다.

그러면 + 에서 - 로 연결되는 전기장이 형성되게 된다.

(아래 그림에서 빨간 선이 전기장)

이 현상은 식각하려는 패턴이 좁고 길어질수록(Aspect ratio가 커질수록) 더 잘 보인다.

그러면 생성된 전기장에 의해 양의 전하를 띄고 있는 Ion은 휘어지게 되어

바닥면에 도달하는 것이 어려워지고 패턴 바닥에 충돌 에너지를 전달할 수 없으므로

결국 식각 진행 속도가 느려지게 되는 것이다.

- 개선하려면?

이온 입사 각도의 divergence 때문에 발생하는 경우, 원자량이 더 무거운 이온(Ar → Kr or Xe)입자를 만들 수 있는 gas를 식각 공정에 사용하거나

Bias power를 상향하는 등의 방법으로 이온의 직진성을 더욱 높여준다면 완화할 수 있을 것이다.

그리고 charging에 의한 이온 입자의 휘어짐 때문에 발생하는 경우,

charge 중성화를 위한 펄스 플라즈마 방법을 사용하여 완화할 수 있다고 한다.

Pulse plasma란 플라즈마를 생성하기 위해 공급하는 Power를 한 cycle에서 일정시간 켜고 끄는 방식이다.

Plasma를 on-off 반복하여 사용하는 것이다.

pulse형태의 사용은 charge 중성화 외에도 여러 이점이 있다고 들었는데 이후 다시 자세히 찾아보아야겠다.

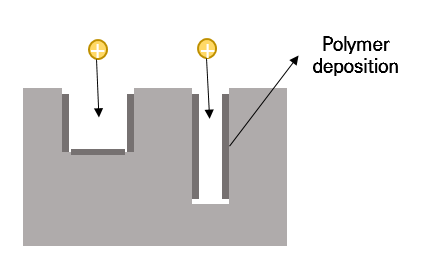

* Inverse RIE lag

추가로, Inverse RIE-lag 현상이 있다.

Inverse RIE-lag 현상은 이름 그대로 RIE-lag 현상의 반대 현상이다.

식각하고자 하는 패턴의 Aspect ratio가 작을수록 식각 속도가 느려지는 현상을 말한다.

식각하려는 패턴의 폭이 넓을 수록 식각 진행 속도가 느리다는 것이다.

이것은 polymer deposition을 이용하여 식각하는 경우에 발생한다.

식각하기 위해 사용하는 gas와 식각하려는 물질 간 화학 반응에 의해 생성된 polymer는 패턴의 옆 벽면에 붙을 확률이 높다.

좁은 패턴의 경우에는 옆 벽면이 길어서 polymer가 벽면에 붙을 확률이 높고,

바닥면은 좁아서 바닥까지 갈 확률은 상대적으로 작다. 그래서 바닥면은 지속적으로 식각이 진행된다.

폭이 넓은 패턴의 경우에는 옆 벽면의 면적이 상대적으로 작기 때문에 바닥면에도 polymer가 붙을 수 있고

그것은 식각의 진행을 방해하게 된다. 그래서 식각 속도가 느려지게 된다.

참고한 논문 :

박완재(2012), 「응용 공정별 맞춤형 플라즈마 건식 식각에 관한 연구」, 서울대학교 대학원.

A Study on customized plasma dry etching suited to various application processes

12년도 논문인데 내가 찾던 내용이 딱 있었다. 박사 논문을 학부생이 제대로 이해할 수는 없겠지만 다른 부분도 잘 읽어보아야 겠다.

★ Etching 공정에서 사용하는 ESC 부품 알아보기

2022.06.15 - [self.반도체&전자회로 공부] - Electrostatic chuck, ESC란?

Electrostatic chuck, ESC란?

Electrostatic chuck, ESC란? 반도체 제조 공정에서 특히 진공을 사용해야 하는 공정(Etching, CVD 공정 등...)의 진행 설비의 경우 ESC 라는 부품은 반드시 장착되어 있고 아마 제일 중요한 부품 중 하나라고

selfimprove39.tistory.com

★ 공정에서 사용하는 RF system 알아보기

2022.07.27 - [self.반도체&전자회로 공부] - RF Matching System과 스미스차트에 대하여(Smith Chart) - 1

RF Matching System과 스미스차트에 대하여(Smith Chart) - 1

RF Matching System와 스미스차트에 대하여(Smith Chart) - 1 반도체 공정 중 Plasma를 사용하여 진행하는 공정이 있고, 그 Plasma를 생성하기 위해서 꼭 필요한 조건 중 하나가 바로 Power다. 그리고 RF power를

selfimprove39.tistory.com

'self.반도체&전자회로 공부' 카테고리의 다른 글

| RF Matching System과 스미스차트에 대하여(Smith Chart) - 2 (0) | 2022.08.02 |

|---|---|

| RF Matching System과 스미스차트에 대하여(Smith Chart) - 1 (0) | 2022.07.27 |

| 식각(etching) 공정에서 profile에 영향을 미치는 loading effect에 대해서 - 1 (1) | 2022.07.08 |

| 반도체 2 - DRAM 과 FLASH 의 차이점은 ? (0) | 2022.06.28 |

| 반도체 1 - 반도체의 종류와 각각의 설명 (0) | 2022.06.25 |