JFET를 이용한 증폭기는 공통으로 사용하는 단자에 따라 공통 소스, 공통 게이트, 공통 드레인 증폭회로가 있다.

공통 소스 증폭기는 전압증폭기(voltage amplifier)로 사용되고 있다.

게이트 단자로 입력신호가 들어가고 드레인 단자로 출력신호가 나온다. 소스 단자는 공통(common, 접지 또는 전원연결) 으로 사용한다.

공통 소스 증폭기(common source; CS)

1. 자체 바이어스 회로 공통 소스 증폭기(self bias) (이전 글 참고)

2. 전압나누기 바이어스 회로 공통 소스 증폭기

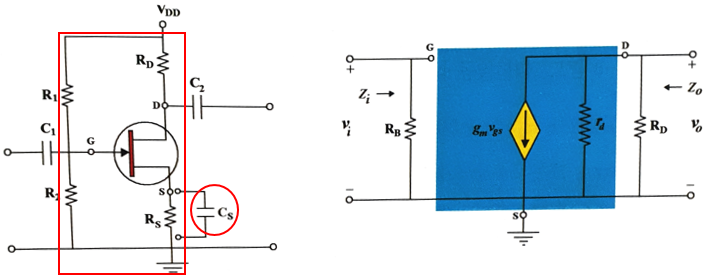

전압나누기 바이어스 회로로 바이어싱 된 공통 소스 증폭기의 회로이다.

공통 소스 증폭기에서는 입력신호는 게이트로 들어가고, 출력은 드레인을 통해 나온다.

소스 저항 옆에 C_S는 우회 축전기이다.

회로에서 직류전원을 모두 없애고 축전기를 제거한 후 FET를 소신호 모델로 대체한 것(빨간선으로 둘러싸인 부분)이 오른쪽 그림이다. 우회축전기 C_S 가 있는 경우이다.

위의 등가회로는 자체 바이어스 공통 소스 증폭기 의 등가회로에서 R_G 를 R_B = (R1 || R2) 로 바꾼 경우와 동일하다.

이에 따라 입력 임피던스에 대한 표현이 Z_i = R_B = (R1 || R2) 로 달라지고 나머지 식들은 동일하게 된다.

여기서 입력 임피던스란 신호원의 저항을 제외하고 연결된 총 저항을 말하고,

출력 임피던스란 부하저항을 제외하고 출력단에 연결된 총 저항을 말하는 것이다.

[참고] 자체 바이어스 공통 소스 증폭기

2022.05.02 - [self 반도체&전자회로 공부] - [트랜지스터 증폭기 회로] JFET를 이용한 소신호(small signal) 증폭기 - 공통 소스 증폭기 1

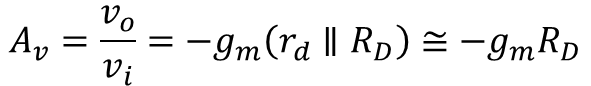

즉, 우회 축전기가 있는 경우 전압 증폭률은 아래와 같이 구해진다.

우회 축전기가 없는 경우의 등가회로는 이 그림이다. 이 등가회로에서 r_d의 효과는 무시하였다.

입력 임피던스는 동일하게 Z_i = R_B 임을 볼 수 있다.

입력부분에서는 v_i = v_gs + g_m*v_gs*R_S 이고, 출력 부분에서는 v_o = -g_m*v_gs*R_D 이므로 전압 증폭률은 아래와 같이 구해진다.

'과학도를 위한 반도체와 전자회로의 기초' 책을 공부하여 작성 하였습니다.

'self.반도체&전자회로 공부' 카테고리의 다른 글

| 뉴로모픽 컴퓨팅(엔지니어링) neuromorphic computing 이란 ? (0) | 2022.05.28 |

|---|---|

| 차세대 반도체 메모리 MRAM - Magnetic Random Access Memory 이란 ? (0) | 2022.05.15 |

| [트랜지스터 증폭기 회로] JFET를 이용한 소신호(small signal) 증폭기 - 공통 소스 증폭기 1 (0) | 2022.05.02 |

| [트랜지스터 증폭기 회로] 트랜지스터의 소신호 증폭기 - 공통 베이스(base) 증폭기 (0) | 2022.04.30 |

| [트랜지스터 증폭기 회로] 트랜지스터의 소신호 증폭기 - 공통 컬렉터(collector) 증폭기 (0) | 2022.04.28 |

댓글