JFET 공통 소스 바이어스 회로

공통 소스 증폭기에서는 입력신호 v_i가 게이트 단자로 들어가고 출력신호 v0가 드레인 단자로 나온다.

소스 단자는 공통(common, 접지 또는 전원연결)으로 사용한다. 전압증폭기로 가장 널리 사용되고 있는 것이 공통 소스 증폭기이다.

공통 소스 증폭기를 위한 바이어스 회로에는 아래 세 가지가 있을 수 있다.

1. 고정 바이어스 회로

2. 자체 바이어스 회로

3. 전압나누기 바이어스 회로

1. 고정 바이어스 회로

고정 바이어스 회로 예시다. 이 회로에서는 n-채널 JFET의 바이어스 전압 V_GS를 공급하기 위해 전원 V_GG를 사용하고 있다. 이 전원에 의해 게이트가 소스에 대해 항상 - 로 유지된다.

이렇게 고정된 전원에 의해 FET가 바이어스되기 때문에 이 회로를 고정 바이어스 회로라고 부른다.

그러나 회로에 표시되어 있는것처럼 게이트전류 I_G = 0 이므로 게이트 저항 R_G를 흐르는 전류가 없다는 것이고, 이 저항에 떨어지는 전압강하도 없다.

즉, 전원 V_GG는 n-채널 JFET의 바이어스 전압 V_GS를 공급하지만 전류를 형성하지는 못한다.

교류증폭기에서는 축전기를 통해 교류신호를 입력시킨다. (직류 신호를 차단하려는 목적도 있음)

이때 저항을 통해 교류신호에 의한 전압강하가 발생하여 게이트에 입력되도록 저항 R_G가 연결되어 있는 것이다.

이 회로의 입력 부분에 Kirchoff 법칙을 적용하면

이고, 여기서 게이트 전류 I_G = 0 이었으므로 전원에 의해 게이트와 소스에는

항상 동일한(고정된) 바이어스 전압 -V_GG가 걸리는 것을 알 수 있다.

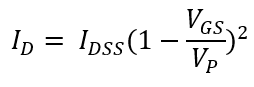

그리고 입력 부분의 키르히호프 식과 JFET 에서의 입력전압 V_GS와 출력전류 I_D와의 관계식(제곱의 관계)을 통해 출력 전류 = 드레인 전류 = I_D를 구할 수 있다.

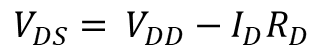

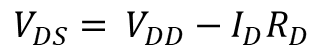

그리고 이 회로의 출력 부분에 Kirchoff 법칙을 적용하면

이므로, 드레인-소스 전압 V_DS 에 대해 다시 정리하면 아래와 같다.

이에 따라 JFET의 동작점 (I_D, V_DS) 가 결정된다.

입력 부분에서 구한 식

직선과

곡선을 표현한 그래프가 왼쪽에 그려져 있다. 이 직선과 곡선이 만나는 지점을 구함으로써 드레인 전류를 구할 수 있다.

출력부분에서 구한 식

드레인 전류와 V_DS 간의 관계를 직선으로 그린 것이 오른쪽 그래프이다. 동작점 Q가 표시되어 있다.

'과학도를 위한 반도체와 전자회로의 기초' 책을 공부하여 작성 하였습니다.

'self.반도체&전자회로 공부' 카테고리의 다른 글

| [FET 바이어스 회로] JFET 공통 드레인 바이어스 회로, 공통 게이트 바이어스 회로 (0) | 2022.04.19 |

|---|---|

| [FET 바이어스 회로] JFET 공통 소스 바이어스 회로 - 자체 바이어스 / 전압나누기 회로 (0) | 2022.04.18 |

| [FET 바이어스 회로] (0) | 2022.04.16 |

| [트랜지스터의 바이어스 회로] 공통 베이스 바이어스, 콜렉터 바이어스 회로 (0) | 2022.04.14 |

| [트랜지스터의 바이어스 회로] 공통 에미터 바이어스 회로 - 3 (0) | 2022.04.13 |