JFET 공통 드레인 바이어스 회로

공통 드레인 바이어스 회로에서는 입력 신호 v_i가 게이트로 들어가고 출력 신호 v_0는 소스 단자로 나온다.

드레인은 공통(common)이다. 이 회로는 양극 접합트랜지스터의 공통 콜렉터 바이어스 회로에 대응된다.

참고

2022.04.14 - [트랜지스터의 바이어스 회로] 공통 베이스 바이어스, 콜렉터 바이어스 회로

입력 부분에 Kirchoff 법칙을 적용하면

인데 여기서 게이트 전류 I_G = 0 이므로

이고, 따라서 게이트-소스 전압은 아래와 같이 구할 수 있다.

그리고 이 회로에서 I_D ≒ I_S 이므로 위의 식은 V_GS = -I_D*R_S 로 바꿔 쓸 수 있고

이를 JFET 에서의 입력전압 V_GS와 출력전류 I_D와의 관계식(제곱의 관계)에 대입하면 아래와 같이 드레인 전류에 대한 2차 방정식을 구할 수 있다.

이 2차 방정식을 풂으로써 드레인 전류 I_D를 구할 수 있다.

마찬가지로 출력 부분에 Kirchoff 법칙을 적용하면

인데 I_D ≒ I_S 를 사용하여 V_DS와 I_D의 관계식으로 다시 정리하면 아래와 같다.

이에 따라 JFET의 동작점 (I_D, V_DS)가 결정된다.

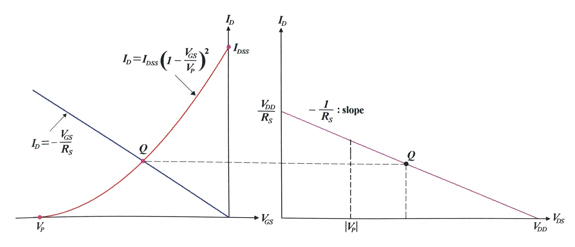

왼쪽 그래프는 입력 부분에서 구한 V_GS와 I_D에 관한 1차 식과 2차 식을 그래프에 타나낸 것이다.

만나는 지점을 구함으로써 드레인 전류를 구할 수 있다.

오른쪽 그래프는 출력 부분에서 구한 V_DS와 I_D간의 1차 식을 그래프에 나타낸 것이다.

동작점 Q가 표시되어 있다.

JFET 공통 게이트 바이어스 회로

공통 게이트 바이어스 회로에서는 입력 신호 v_i가 소스 단자로 들어가고, 출력 신호 v_0는 드레인 단자로 나온다.

게이트는 공통(common)이다. 이 바이어스 회로는 양극 접합트랜지스터의 공통 베이스 바이어스 회로에 대응된다.

입력 부분에 Kirchoff 법칙을 적용하면(소스 단자가 있는 부분)

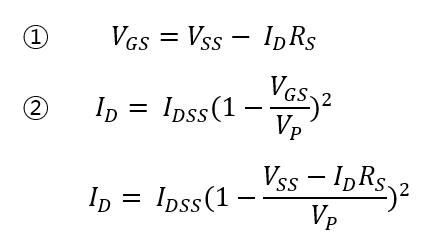

이고, I_D = I_S 이므로 아래와 같이 V_GS와 I_D에 관한 1차 식으로 정리할 수 있다.

이를 JFET 에서의 입력전압 V_GS와 출력전류 I_D와의 관계식(제곱의 관계)에 대입하면 아래와 같이 드레인 전류에 대한 2차 방정식을 구할 수 있다.

이 식은 드레인 전류에 대한 2차 방정식이므로 이를 풂으로써 I_D를 구할 수 있다.

그리고 전체 폐회로에 대해 Kirchoff 법칙을 적용하면

인데, I_D = I_S 이므로 다시 정리하면 아래와 같이 V_DS와 I_D에 대한 식을 구할 수 있다.

이 1차 식에 따라 JFET의 동작점 (I_D, V_DS)가 결정된다.

왼쪽 그래프는 입력 부분에서 구한 V_GS와 I_D에 관한 1차 식과 2차 식을 그래프에 타나낸 것이다.

만나는 지점을 구함으로써 드레인 전류를 구할 수 있다.

오른쪽 그래프는 출력 부분에서 구한 V_DS와 I_D간의 1차 식을 그래프에 나타낸 것이다.

동작점 Q가 표시되어 있다.

'과학도를 위한 반도체와 전자회로의 기초' 책을 공부하여 작성 하였습니다.

'self.반도체&전자회로 공부' 카테고리의 다른 글

| [트랜지스터 증폭기 회로] 트랜지스터의 소신호 모델 - 양극 접합트랜지스터 소신호 모델 1 (0) | 2022.04.22 |

|---|---|

| [FET 바이어스 회로] 공핍형, 증가형 MOSFET 의 전압나누기 바이어스 회로 (0) | 2022.04.20 |

| [FET 바이어스 회로] JFET 공통 소스 바이어스 회로 - 자체 바이어스 / 전압나누기 회로 (0) | 2022.04.18 |

| [FET 바이어스 회로] JFET 공통 소스 바이어스 회로 - 고정 바이어스 회로 (0) | 2022.04.17 |

| [FET 바이어스 회로] (0) | 2022.04.16 |